Global Semiconductor Alliance

LEADERSHIP THROUGH GLOBAL COLLABORATION

IS YOUR SUPPLY CHAIN READY FOR AN ECONOMIC RECOVERY?

HIDDEN LOGISTICS AND FULFILLMENT COSTS IN THE SEMICONDUCTOR SUPPLY CHAIN

WHAT'S YOUR RETURN ON DEVELOPMENT? IDENTIFYING THE KEY LEVERS AND MOVING THE NEEDLE

INTERNATIONAL CHALLENGES IN ENVIRONMENTAL COMPLIANCE AND SUPPLY CHAIN SUSTAINABILITY

**The First Truly Global Foundry**

**TOSHIBA**

SYNOPSYS

MAGMA

**MEDIATEK**

Congratulations to the new GLOBALFOUNDRIES, the merged operations of GLOBALFOUNDRIES and Chartered.

To our continued mutual success from your Global Customers and Partners

#### 2 Leadership through Global Collaboration

Kerry Enright, President, Enright Enterprise Consulting Solutions LLC

6 Is Your Supply Chain Ready for an Economic Recovery?

Jim Takach, Director, PRTM

11 Hidden Logistics and Fulfillment Costs in the Semiconductor Supply Chain Marta Garcés, Vice President, Operations, ADD Semiconductor

15 International Challenges in Environmental Compliance and Supply Chain

Tom Krawczyk, Compliance Manager, Conexant Systems Inc. Bob Warren, Director, Packaging Engineering & Assembly Manufacturing, Conexant Systems Inc.

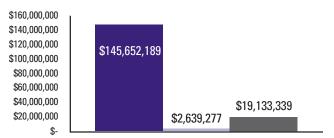

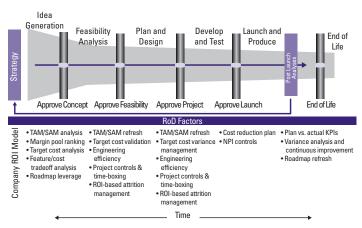

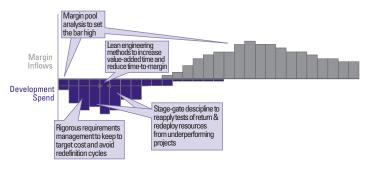

19 What's Your Return on Development? Identifying the Key Levers and Moving the Needle

Mark Davis, Principal, Deloitte Consulting LLP John La Bouff, Senior Manager, Deloitte Consulting LLP

23 Getting the Most out of a Yield Management System

Nancy K. Tsai, President, Nancy K. Tsai Consulting

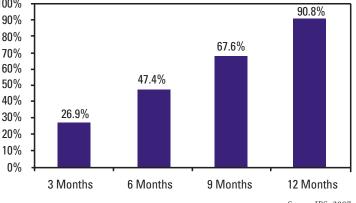

27 Hardware Emulation Proven to Reduce the Cost of Bringing a Chip to Market Lauro Rizzatti, General Manager, EVE-USA

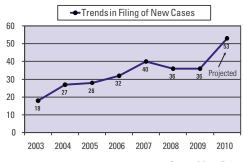

30 How Semiconductor Companies Are Helping Counterfeiters

Chris Jensen, Vice President, New Momentum

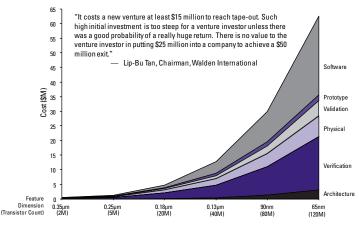

32 Cost Realities in Bringing a Chip to Market

Sanjay Krishnan, Business Manager, High-performance Analog Group, Maxim Integrated Products

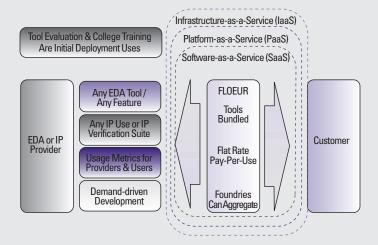

35 On-demand Tool and IP Grid: Examining the Merits of Fully Leasable On-demand **Engineering Utility Resourcing**

Camille Kokozaki, President, Design Rivers

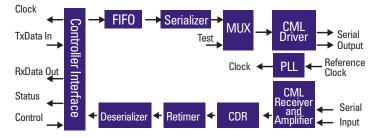

37 The Future of Mobile Electronics Interconnectivity

Hezi Saar, Senior Manager, SiPro Advanced Interface IP Product Line, Virage Logic

#### IN EVERY ISSUE

- 4 Semiconductor Member News

- 8 Foundry Focus

- 13 Back-End Alley

- 17 Supply Chain Chronicles

- 21 Global Market Trends

- 25 Industry Reflections

- 28 Global Insights

- 34 Private Showing

- 39 Innovator Spotlight

#### INTERESTED IN CONTRIBUTING TO THE GSA FORUM?

To contribute an article, contact: Chelsea Boone, GSA Forum Executive Editor, cboone@gsaglobal.org. To advertise, contact: Monica Dominguez, Advertising Executive, mdominguez@gsaglobal.org = GSA = 12400 Coit Road, Suite 650, Dallas, TX 75251 = phone 888.322.5195 • fax 972.239.2292

ACCELERATE THE **GROWTH AND** INCREASE THE RETURN ON INVESTED CAPITAL OF THE GLOBAL **SEMICONDUCTOR** INDUSTRY BY FOSTERING A MORE EFFECTIVE FABLESS **ECOSYSTEM** THROUGH COLLABORATION. INTEGRATION AND INNOVATION.

- Address the challenges and enable industry-wide solutions within the supply chain, including intellectual property (IP), electronic design automation (EDA)/design, wafer manufacturing, test and packaging

- Provide a platform for meaningful global collaboration

- Identify and articulate market opportunities

- Encourage and support entrepreneurship

- Provide members with comprehensive and unique market intelligence

### LEADERSHIP THROUGH GLOBAL COLLABORATION

KERRY ENRIGHT, PRESIDENT, ENRIGHT ENTERPRISE CONSULTING SOLUTIONS LLC

he semiconductor industry leads the world in innovation, leveraging global partnerships as one of its keys to success. Yet is the industry really living up to its potential? To surmount current economic difficulties, the industry struggles to regain its momentum in leadership solutions through its various partnerships, but often these results fall short. The real problem, it appears, is that the industry focuses on partnerships but not true collaboration. What is the difference?

Working my way through college, I earned money by partnering on construction projects. In the first project, my partner and I started a block wall from different ends and worked towards each other. Upon meeting in the middle, we discovered that we had created a disaster. We changed our approach so that we always started at the same end, alternating mortaring and setting the block along our mutual guideline. As the wall rose, we arranged our staging to enable us to remain face to face and task to task through completion. This typified the essence of collaboration.

Our collaboration succeeded on the following elements:

- Standardized material of exchange.

- A mutual guideline.

- A common, real-time and interactive process.

How can semiconductor executives create such collaboration on a global basis, when in their own buildings their engineers on the first floor do not share processes with their engineers on the second? Since programs falter on the basics, how can collaborators deliver the right process to the right people at the right time?

#### The Shortcomings of Partnerships

Partnerships are plentiful in the semiconductor industry, but these partnerships struggle with execution challenges.

#### Standardized Material of Exchange

The most basic material of exchange, the document, can create execution barriers. There was a case where the engineer of a foreign partner sent the U.S. partner a design document that the U.S. partner believed to be approved. Based on this, they commenced their development. When the foreign partner's executives later denied that the design document was approved or supported, the U.S. partner backtracked on their development, losing months of development. Document exchange with multiple partners through team rooms creates similar vulnerabilities.

Partnerships seldom standardize their medium of exchange by defining the following:

- The document state: draft, preliminary, approved and released.

- The document version: V1.0 Vn.n.

- The document status: in development, idle, in approval and in rework.

- The document location: physical and logical.

Without these basics, partners struggle as if they are working on opposite sides of a high wall.

Similarly, data is a fundamental material of exchange. While some partners succeed in creating common data dictionaries using naming conventions and formats, the challenges do not end there. Equally important, partners must facilitate data access. Eliminating "data rummaging" requires systems to capture, store and transfer fab process data to the right users based on who owns what data, what data is to be shared and what remains proprietary.

#### A Mutual Guideline

In construction, a taut guideline aligns processes to produce correct results. The same applies to the semiconductor industry, but the guideline contents are more complex—ground rules, specifications, intellectual property (IP) and assets.

Partnerships often fail to create common guidelines that produce the right results. How often do partners fail to agree on whether to use industry-standard design ground rules versus their own proprietary rules, when even something as simple as standardizing built-in self-test (BIST) greatly enhances a design? Guidelines on which design tool to use are likewise critical since different tools can produce different results to the same design problem.

Controlling specifications is a multi-headed task of creation, management and use. All specifications must reflect end-client needs, and since partners have different client views, they must create a coherent client advocacy within a joint management structure. This structure must compile and codify specifications before design start. Finally, a mutual guideline must decompose, disseminate and insert the specifications into each branch and level of design.

As with specifications, IP requires acquisition with the end client in mind. Since IP acquisition requires very extensive lead times, it must be planned far in advance. Individual companies typically field more requests for IP than they can afford, so partners working in conjunction need to coordinate their IP strategic plans if IP is to arrive just in time. Likewise, partners must support IP providers with standardized and common business engagement processes.

Partnerships imply sharing; and the more the partners share, the more critical becomes the relationship. But whenever sharing is involved, issues of value arise. Consider this. When multiple companies come together, they naturally attach a value to the assets they bring to the common table. How then do the partners assess the value of what they and their partners offer so that all parties believe they received an equitable deal? This question escalates as the number of participants goes up. It also arises with IP acquisitions where the perceived value varies among the partners.

#### A Common, Real-Time and Interactive Process

Global partnerships exist to deliver converged products at a quality and cost attractive to clients. Unfortunately, many programs fail at the very beginning because of shortcomings in execution. Of these shortcomings, two stand out—client and manufacturing engagement.

The semiconductor industry resonates to extremely time-sensitive client demands, and new projects often start under severe schedule pressures. Frequently, this schedule pressure influences many partnerships to short cut the initial and most critical part of the program—concept and requirements definition. A poorly defined project concept or client requirements ripple down the design process and often result in project churn or design re-spins. Missed client requirements result in failed products.

Similarly, partner teams may lack assurance at program initiation that the designs are actually manufacturable across their disparate facilities. An obvious resolution to this problem engages manufacturing teams at the very outset of the program, but this approach proves cumbersome across multiple companies and is often omitted from program definition.

Once programs are underway, clear, formal reviews and handoffs between stages become paramount to ensure end-to-end linkage. Unless, however, the partners standardized their program linkages before the start, there is a high probability that broken couplings will plague their efforts.

The cash cow of the semiconductor industry thrives upon technology reuse—extending last-generation technology into incremental marketplaces. The secret to reuse is the creation of viable variants out of a common technology. Common technology, in turn, arises from disciplined design and manufacturing processes. Many semiconductor companies find maintaining a common technology challenging even for in-house needs, but when the opportunities extend over multiple companies, the task becomes exponentially more difficult.

Finally, companies evolve and even partners' strong initial commonality efforts face the prospect of divergence over time. Any attempt at cooperation, therefore, must also include plans for continuation.

#### Opportunities for Collaboration

If global collaboration requires standardized material of exchange, a mutual guideline and a common, real-time and interactive process, how can semiconductor executives create capabilities out of their disparate environments? The following highlights a method.

#### Process Management - Standardized Material of Exchange

Collaboration provides opportunities for standardizing materials of exchange. Since most companies have entrenched methodologies inherently resistant to change, introducing a collaborative environment opens the door to new methods—a superset of the individual companies. Operational executives can leverage their joint relationship to win greater degrees of freedom in standardizing common process exchange.

#### Process Standardization

Step one is to create simplicity in the face of complexity. Standardization of building materials enabled the efficient construction of homes and offices from worldwide product sources. The same principle applies to collaborative business processes.

Companies can standardize processes in the following manner:

- Radically reduce process logic into the simplest model that always delivers complete, correct and timely execution.

- Create a building block out of that model by embedding standard management functions.

- Tailor building blocks to specific tasks using pre-defined bestof-breed process templates.

- Construct maxi-enterprise execution logic out of the building blocks.

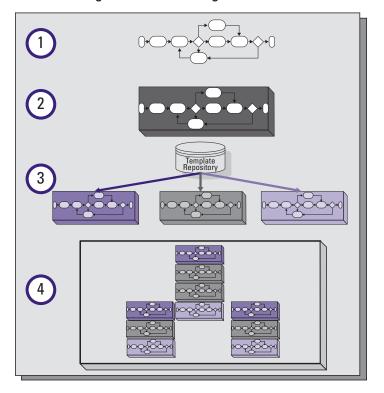

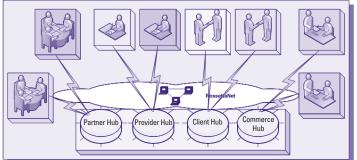

Figure 1. Process Management Method

Note that the Figure 1 structure is not an application but an engine. Applications wait for instructions that derive from the enterprise execution logic. Engines embody enterprise execution logic and summon applications for procedures and functions that fulfill the logic.

#### Process Universals

All processes require a basic suite of functions to achieve complete, correct and timely execution. These functions manage state, version, status and location of any document, program or program subcomponent. Additionally, performance monitoring provides essential support for process control and continuous improvement. By packaging such elements within process models, alliance participants can create execution hubs.

#### Execution Hubs - Mutual Guidelines

Execution hubs create mutual guidelines for classes of users. Every cooperative enterprise is nothing if not a collection of interested

Actel's (NASDAQ: ACTL) radiation-tolerant RTAX digital signal processor (DSP) field-programmable gate arrays (FPGAs) have completed qualification in accordance with the military and aerospace industry standard MIL-STD-883 Class B specification. This qualification expands Actel's support of high-speed signal processing applications for space payloads and exemplifies its ongoing innovation and commitment to serve designers of spaceflight systems.

Advanced Analogic Technologies (NASDAQ: AATI) introduced the AAT282X active matrix thin-film transistor (TFT) liquid crystal display (LCD) direct current/direct current (DC/DC) converter family which includes a white light-emitting diode (WLED) driver and VCOM buffer to enable the delivery of a fully integrated power solution for portable backlit displays. Key target applications include automotive displays, digital photo frames, netbooks, e-readers and handheld global positioning system (GPS) navigation devices.

Altera (NASDAQ: ALTR) enhanced its Arria II GX FPGA variant with 6.375 Gbps transceivers and up to 1.25 Gbps low-voltage differential signaling (LVDS) support, while broadening the reach of the family with the addition of the new Arria II GZ FPGA variant. As a result, the 40 nm Arria II family provides the lowest power 6 Gbps transceiver solutions shipping today, featuring up to 50 percent lower static power over competitive devices.

The newest member of the **Broadcom** (NASDAQ: BRCM) Intensi-fi product family revolutionizes how users can experience multimedia content in their homes. The BCM4331 Wi-Fi solution achieves 450 Mbps data rates in client devices and over 600 Mbps throughput (Transmission Control Protocol/Internet Protocol (TCP/IP)) in 3x3 access point (AP)/router configurations.

Skelmir has ported their CEE-J virtual machine (VM) to Cavium Networks' (NASDAQ: CAVM) ECONA CNS3XXX processors for the support of Open Services Gateway Initiative (OSGi) and other Java applications. The ECONA CNS3XXX family of ARM-based energy-efficient processors offers single and dual ARM11 MPCore processors, a rich set of integrated hardware accelerators and a range of inputs/outputs (I/Os) for glueless voice, video and data connectivity.

CHiL Semiconductor announced a breakthrough in high-efficiency computing voltage regulator (VR) solutions for central processing unit (CPU), graphics processing unit (GPU) and double data rate (DDR) applications. Now configured to optimize efficiency from the lowest idle state to the highest operating state of today's high-performance server, graphics and desktop

solutions, CHiL's next-generation truedigital power algorithms have increased efficiency up to 15 percent, especially at low loads.

Cortina Systems introduced CS4340, the industry's smallest quad 10 GB electronic dispersion compensation (EDC) device. The Cortina CS4340 is a programmable four-port small form-factor pluggable physical layer (SFP + PHY) with integrated EDC and is available in a small 15 mm x 15 mm ball grid array (BGA) package that optimizes system design options.

Fujitsu Limited selected **Cypress Semiconductor's** (NASDAQ: CY) TrueTouch solution to implement the touchscreen in the world's first separable handset from NTT DOCOMO, the DOCOMO PRIME series F-04B mobile phone. The new phone leverages Cypress' CY8CTMG200 controller to power the robust multi-touch interface with a slim 9.8 mm form factor that can operate separately from the keyboard.

Dialog Semiconductor DLG) signed a licensing agreement to use NXP's ultra low-power embedded digital audio signal processor technology, CoolFlux DSP, and accompanying firmware, including NXP Software's LifeVibes voice speech enhancement engine. The move by Dialog is the next step in a strategic initiative to develop and deliver market-leading standalone and integrated power management and audio ICs with highly differentiated feature sets. Integration of the NXP DSP allows multiple audio decoding algorithms to be supported, including the facilitation of advanced speech processing algorithms.

**Discera** announced the official opening of its China Applications Center in the Shenzhen International Chamber of Commerce Tower on Fuhua 3rd Road, Futian District. As the heart of the company's permanent investment plan in China, the new office features engineers, equipment and researchers to support sophisticated chip and module integration, high-definition (HD) and 3-D video technology, and radio frequency (RF) and smart grid design.

To enhance the growth of the universal docking station market, ASUS has chosen to integrate **DisplayLink's** Universal Serial Bus (USB) virtual graphics processor, the DL-165, into the ASUS USB universal docking station.

Exar (NASDAQ: EXAR) introduced the DX 1700 series of Peripheral Component Interconnect (PCI) Express-based cards for the emerging unified storage and network infrastructure. The DX 1700 series is comprised of four cards and offers customers the industry's most power-efficient encryption and compression solutions addressing the small office/home office (SOHO) to enterprise markets.

Fresco Microchip was recently recognized as the fastest growing fabless semiconductor company in the industry. In June, Fresco announced that it has ramped from initial production to more than 15 million chips for the hybrid television market in less than three quarters. Eight of the top 10 TV tuner manufacturers are now in production or have active designs using Fresco inside, including LG Innotek, Panasonic Electronic Devices, NuTune and most recently Sanyo Tuner. According to industry experts, the company will be a top supplier of hybrid television receivers in Europe this year.

Gennum (TSX: GND) announced that its serial digital interface (SDI) solutions have been selected by Panasonic for use in industry-leading professional quality 3-D video equipment. With 3-D TV growth outpacing that of HDTV, demand for 3-D programming and content is on the rise.

NETGEAR selected **Gigle Networks'** GGL301 HomePlug AV/Institute of Electrical and Electronics Engineers (IEEE) 1901 solution with Xtendnet intelligent switching technology to give its XAV101V2 powerline adapters bestin-class network coverage and reliability in the home.

**GigOptix** (OTCBB: GGOX) made additional shipments of its LX8900, a 100 GB thin-film polymer-on-silicon (TFPS) modulator, to a number of customers including SA Photonics, an engineering company focused on photonics-based solutions for military applications.

Icera announced that its Livanto chipset and adaptive wireless technology is at the heart of Vodafone's latest mobile broadband USB stick, the Vodafone K3805-Z. Offering a high-speed mobile broadband connection with theoretical peak downlink rates of up to 14.4 Mbps High-Speed Packet Access (HSPA) in optimal conditions, the Vodafone K3805-Z is the world's first USB modem to incorporate Icera's IceClear interference-aware technology.

Digital China Holdings Limited will distribute **Impinj's** Speedway family of radio frequency identification (RFID) reader and antenna products throughout China. The new relationship ensures that Chinese RFID solution providers now have easy access to the world's leading ultra-high frequency (UHF) Gen 2 technology for a wide variety of applications and markets.

Infineon Technologies AG (FSE: IFX) introduced an enhanced family of three wireless control receivers offering the highest available sensitivity and low-power consumption. The TDA5240, TDA5235 and TDA5225 devices provide multi-band support for worldwide coverage and are well-suited for use in various automotive applications,

including remote keyless entry (RKE) systems, tire pressure monitoring systems (TPMS), remote start, control, status and alarm functions.

Innovasic Semiconductor unveiled its new RapID Platform connectivity solution for EtherNet/IP adapters. Innovasic's RapID Platform provides quick and easy EtherNet/IP connectivity, and engineers can download the entire platform free of charge for evaluation. A one-time license fee applies only if the platform is used in production.

International Rectifier (NYSE: IRF) introduced a family of hexagonal fieldeffect transistor (HEXFET) power metaloxide semiconductor field-effect transistors (MOSFETs) featuring ultra-low on-state resistance (RDS(on)) in an industry-standard small-outline transistor (SOT)-23 package for applications including battery charge and discharge switches, system and load switches, light load motor drives and telecom equipment. Utilizing IR's latest mid-voltage silicon technology, the new SOT-23 MOSFET devices deliver a strong improvement in current handling by minimizing Rds(on) by as much as 90 percent to offer customers optimized performance and price for a given application.

AdaptivEnergy partnered with **Jennic** to offer alternative energy solutions for active RFID tag applications that can offset associated costs and risks inherent with battery-powered devices. Jennic's asset tracking platform uses IEEE802.15.4 technology to provide a robust active RFID solution with low-power requirements, allowing for tags with extended battery life or tags powered solely by harvested energy.

LSI (NYSE: LSI) and Seagate announced the delivery of a complex integrated read channel technology for Seagate's latest hard disk drive (HDD) products. Together, the companies have enabled the industry's first HDDs with low-density parity check (LDPC) read channel in 65 nm process system-on-chip (SoC) technology.

MediaTek (TSE: 2454) joined the Open Handset Alliance. Sharing the same commitment and vision for richer mobile living, the Open Handset Alliance is a partnership of more than 71 global mobile industry leaders aimed to accelerate innovation and offer consumers a richer and connected mobile experience.

Mellanox Technologies' (NASDAQ: MLNX) ConnectX-2 InfiniBand adapters and IS5000 InfiniBand switches have demonstrated world-record Message Passing Interface (MPI) performance for node-to-node communications. Recent cluster benchmarking performed at Mellanox's performance optimizations lab highlights Mellanox InfiniBand's achievement of nearly 90 million messages per second for MPI message rate for node-to-node communications, more than three times better than other comparable InfiniBand solutions.

Microsemi (NASDAQ: MSCC) unveiled a compact, cost-effective four-port power-over-Ethernet (PoE) midspan designed to power a wide range of network devices in low-density applications. Microsemi's new PowerDsine PD-3504G midspan is fully compliant with IEEE 802.3af specifications to safely power wireless local area network (WLAN) APs, IP security cameras, voice over IP phones, access control systems and other devices over existing standard Ethernet cabling.

**Nanoradio** launched NRX600/605, the Eco-Fi family of products. Nanoradio is now able to significantly strengthen its customers' products and further enrich the user experiences of embedded consumer electronics powered by the new solution. The product family, which is supporting 802.11 b/g/n standards, gives outstanding power and area savings, unwiring new economically and ecologically innovative customer products.

Nordic Semiconductor ASA (OSE: NOD) released nRFready R/C Racing, a complete reference design for advanced remote controlled racing toys that enables toy manufacturers to bring previously impossible game-play features to mass-market toys by using Nordic's low-cost 2.4 GHz wireless solutions.

Octasic announced the industry's most efficient multi-core DSP device for basestation PHY and Media Access Control (MAC), the OCT2224W. Delivering three times more power efficiency than any other DSP on the market today, the OCT2224W device provides the best performance-to-power ratio in the industry.

ParkerVision (NASDAQ: PRKR) entered into an agreement with its confidential baseband partner to supply RF chipsets that incorporate ParkerVision's d2p technology. The chipsets will be used with baseband processors sold to a leading mobile handset original equipment manufacturer (OEM) who is a significant customer of ParkerVision's baseband partner.

PMC-Sierra (NASDAQ: PMCS) announced the SRCv family of 6 Gbps Serial Attached Small Computer System Interface (SCSI) Redundant Array of Independent Disks (RAID)-on-chip (RoC) controllers, including the industry's first 24-port RoC, which enables the highest levels of server performance and connectivity, along with an eight-port RoC targeted at the volume x86 server market.

Qualcomm (NASDAQ: QCOM) and Medical Platform Asia signed a formal agreement to provide medical devices with integrated 3G wireless modules for people in need of health services. The project is being implemented through Qualcomm's Wireless Reach initiative and will allow 300 remote local residents to send critical health information to doctors through a 3G wireless network. Information such a resident's blood pressure, weight and distance walked can be easily and immediately shared with participating physicians.

RF Micro Devices (NASDAQ: RFMD) announced the RF5616, a highly integrated 4.9 GHz to 5.8 GHz (industrial, scientific and medical (ISM) band) 3 mm x 3 mm power amplifier designed to significantly reduce customers' total solution size and cost. The RF5616 is targeted for high-performance mobile PC and embedded applications including APs, gateways, digital subscriber line (DSL) routers, Wireless High-Definition Interface (WHDI) and WLAN for wireless video distribution networks.

Sigma Designs (NASDAQ: SIGM)

announced the first low-cost Microsoft Mediaroom-compatible set-top box (STB) platform based on Sigma's SMP8652 media processor SoC. SMP8652-based STB designs have completed integration with Mediaroom client software and are anticipated to begin deployment with leading carriers in 2H 2010.

Samsung Electronics is leveraging one of **Skyworks Solutions'** (NASDAQ: SWKS) power amplifier modules for the GT-B3710, a high-speed 4G USB modem that is the world's first Long-Term Evolution (LTE)-commercialized device. Small and efficient, the SKY77706 LTE power amplifier (PA) module is designed for multiple handset and data card applications, and allows consumers to enjoy the benefits of high-speed data services such as advanced Web TV broadcasting, online gaming and Web conferencing.

Toshiba America Electronic Components (TSE: 6502) and its parent company Toshiba launched a 128 GB embedded NAND Flash memory module, the highest capacity yet achieved in the industry. The module is fully compliant with the latest embedded-MultiMediaCard (e-MMC) standard, and is designed for application in a wide range of digital consumer products, including smartphones, tablet PCs and digital video cameras.

**Ubicom** introduced its IP8100 family of network processors. The processors are targeted towards next-generation solutions for consumer, SOHO and small/medium business (SMB) applications for both retail and service provider deployments.

VIA Technologies (TSE: 2388) released device development kits for the VIA AMOS-5000 series, facilitating a more rational design infrastructure for a broad range of application-specific and fan-less Em-ITX-based devices. VIA AMOS-5000 series development kits combine application-specific VIA EM-I/O expansion modules with specially designed extendable aluminum chassis kits.

**WiSpry** is working with IBM to develop micro-electromechanical systems (MEMS) process technology and manufacture its tunable RF product roadmap. This development includes WiSpry's current generation of tunable impedance matching products, slated for production with a major Tier-1 OEM this fall, as well as future generations of highly integrated products for the entire mobile terminal front-end.

Xelerated sampled its HX family of network processor units (NPUs), which are now available to system vendors and service providers. Based on Xelerated's unique and deterministic dataflow architecture, the HX family of NPUs can process 100 Gbitps of Ethernet traffic at wirespeed for any packet size.

ChipSiP Technology and **Zoran** (NASDAQ: ZRAN) collaborated to produce a new slim package solution for the compact digital camera market that includes both multi-memory and an image processor. This new packaging solution helps designers save space on digital camera design boards and shorten the interconnection distance between electric components, significantly improving performance.

## Is Your Supply Chain Ready for an Economic Recovery?

JIM TAKACH, DIRECTOR, PRTM

ompanies across many industries believe that the worst of the downturn has come to an end. After making massive cutbacks over the past couple of years, they are starting to see an increase in demand. This development is good for semiconductor companies, but it also presents some significant challenges.

According to PRTM's recent global survey<sup>1</sup>, companies across many sectors, on average, expect their revenues to grow more than 8 percent annually through 2012. More than one third of the companies surveyed expect average gross margins to exceed 20 percent by 2012; two thirds expect gross margins to surpass 10 percent. While the responses vary by industry, the numbers as a whole stand in strong contrast to just a year ago, when many companies experienced flat or declining sales and struggled to produce profits.

But are supply chains ready for the upturn? Many executives doubt their companies have the capabilities needed to meet rising demand and the greater complexity it will impose on the supply chain.

The findings of this year's survey throw light on the concerns that companies are experiencing as they prepare for the economic recovery. A significant number of the survey's nearly 350 respondents were original equipment manufacturers (OEMs) and suppliers from major sectors served by semiconductor companies, including the electronics, communications, industrial equipment, medical device, automotive, and aerospace and defense industries. Given the end-to-end nature of today's supply chains, the challenges that customers face are as important for semiconductor companies to understand as the ones they face themselves.

#### **Key Survey Findings**

This year's survey revealed five key themes:

#### Supply Chain Volatility and Uncertainty Are Here to Stay

Nearly 75 percent of all survey respondents consider demand volatility and poor forecast accuracy the greatest supply chain challenge. Additionally, nearly 25 percent said supplier quality and on-time delivery were major concerns.

During the recession, customer buying patterns changed dramatically and became even more difficult to predict. As companies slashed prices and end customers focused more on value, demand volatility grew, making accurate forecasting increasingly difficult. This behavior will likely continue. And even in cases where demand improves, the capacity cutbacks that suppliers enacted to weather the downturn have made it difficult to ramp-up production.

To address these challenges, semiconductor companies need to ensure they have visibility as far "downstream" in the supply chain as possible. Both they and their customers must strengthen capabilities to effectively plan and respond to changes in demand. This requires solid management processes, strong organizational capabilities, and the right systems and tools.

### Securing Growth Requires Global Customer and Supplier Networks

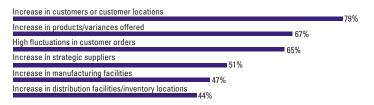

The survey suggests that global expansion and customized products will be key sources of future growth. More than three fourths of respondents anticipate an increase in the number of international customer locations, and more than two thirds expect an increase in the number of products or product variants to address future market needs. And, notably, more than 85 percent expect the complexity of their supply chains to increase significantly by 2012.

To overcome these hurdles, companies must make sure that their global supply chain networks are designed to cost effectively serve the evolving market base, and that their supply chain organizations have the capabilities needed to manage these networks. This requires staying close to customers and to their customers' customers—critical for keeping up with changing supply chain footprints.

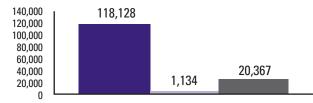

Figure 1. Drivers of Supply Chain Complexity

Percentage of participating companies expecting an increase (multiple answers possible)

### Market Dynamics Demand Regional and Cost-optimized Supply Chains

Outsourcing is on the rise as companies try to cut supply chain costs and increase flexibility. When asked what they keep in-house versus what they outsource, companies surveyed said they outsource 40 percent of their warehousing and transportation, about 30 percent of their manufacturing and nearly 25 percent of their final assembly. Although outsourcing has provided significant labor and material savings, many companies did not report reductions in process or management costs.

Outsourcing is an effective strategy for reducing operating costs, but additional overhead may be required to manage these operations. Companies need to get a better handle on the management and process costs that can fly under the radar. Total supply chain cost engineering is a useful tool in this regard.

#### Companies Must Take a Broader Approach to Supply Chain Risk Management

The survey results indicate that managing risk across the entire supply chain—from demand planning to expansion of manufacturing capacity—is an imperative. Respondents noted that effective risk management requires a multifaceted strategy. Nearly 70 percent said that additional risk mitigation strategies, such as steps to improve inventory management and delivery performance, were at the top of their agenda. These focus areas are part of a much broader approach to supply chain risk management, as customer companies shift more risks upstream to their suppliers.

This approach marks an important departure from the recent past. During the global financial crisis, many companies concentrated their efforts on minimizing the risk of supplier defaults and other issues with the potential to disrupt supply quality and delivery. While this is still a priority, it does not rank as highly as other risk mitigation strategies.

In view of these findings, supply chain executives must take an end-to-end view of risk management—from demand planning to the extended supply chain footprint. They should include not only the internal supply chain organization, but also supply chain partners—OEMs and suppliers—when forming supply chain risk management strategies. This is vital for companies throughout the value chain.

Figure 2. Top Strategies to Reduce Risk and the Negative Impact of the Downturn

% of participants that pay significant attention to the following risk mitigation strategies by 2012

### Existing Supply Chain Organizations Are Not Equipped for the Challenges Ahead

Problems with the supply chain organization stand in the way of many companies wishing to capture the benefits of the recovering economy. Nearly 30 percent of respondents indicated their supply chain organizations lack the integration and collaboration needed to ensure that decisions are optimal for all supply chain functions. And nearly 25 percent indicated their organizations are unable to make decisions quickly in response to sudden changes in demand.

Leading companies across industries understand that breakthrough improvements mandate the integration of key functions, such as product development and manufacturing, and their close collaboration in areas such as new product introductions and ongoing lifecycle management. These companies also make sure to empower their supply chain managers so they can facilitate

optimal decisions and execute end-to-end improvements.

Semiconductor companies would be well-served adopting these practices. In the future, corporate performance depends increasingly on a supply chain organization which effectively collaborates with other business units, and which maintains clearly defined roles and accountabilities, and strong talent.

#### Industry-Specific Findings

The findings for the automotive, electronics and communications, and industrial sectors—many of which rely heavily on semiconductor products and services—are also worth noting.

#### **Automotive**

Today's outlook for the automotive sector is rosier than recent years as automotive companies expect increasing customer demand for a generation of cars that provide higher fuel efficiency, in-car entertainment and other features. Survey participants from the automotive industry expect 9 percent annual revenue growth over the next three years and average gross margins to surpass 10 percent by 2012.

While demand volatility is a challenge for automotive, in some ways the sector is better prepared than others to address it. A high number of automotive respondents indicated they have streamlined product development and manufacturing processes and have adopted strong modularity standards and component standardization—all of which enable a flexible response to market changes.

#### **Electronics and Communications**

Companies in these sectors are optimistic about financial health: Nearly half expect gross margins of at least 20 percent by 2012. Optimism is greatest in companies based in Asia and Europe.

Nearly 90 percent of electronics and communications respondents indicate demand volatility and forecast accuracy to be a major challenge. Response strategies include cycle-time reduction, component and module standardization, joint planning with customers, better demand sensing, and improvements to warehousing and logistics.

The sector also sees continued cost pressures. To achieve the needed reductions, companies envision further outsourcing of manufacturing, warehousing and logistics, and after-sales service and repair.

#### Industrial

More than 80 percent of industrial respondents said demand volatility is a major concern. Not coincidentally, the survey also indicated that industrial companies' demand forecasting is in need of significant improvement. One third of respondents update forecasts with their key customers only once a quarter, and nearly half do so once a month. These companies would do well to follow the example of leading companies which update their forecasts more frequently.

Manufacturing flexibility is also a priority. More than 90 percent of manufacturing respondents plan to focus on cycle-time reduction, and nearly 80 percent are moving to a make-to-order strategy. These companies also highlighted continued focus on supplier lead times and capacities.

austriamicrosystems recently celebrated the 4th anniversary of high-volume production of its best-in-class 120 V 0.35  $\mu$ m high-voltage CMOS process. Successfully introduced already in May 2006, foundry customers benefit from a fully qualified, high-volume production-proven and mature high-voltage CMOS technology ideally suited for emerging applications such as sensor interfaces, power-over-Ethernet (PoE), motor controllers and a variety of automotive applications.

The H35 specialty foundry technology allows the integration of 3.3 V, 5 V, 20 V, 50 V and 120 V n-type metal-oxide semiconductor (NMOS) and p-type metaloxide semiconductor (PMOS) devices on a single chip without any process changes. H35 is the first purely CMOS-based highvoltage foundry process that matches bipolar/ CMOS/DMOS (BCD) performance and chip sizes at much lower process complexity. Rigorous modularity permits 100 percent reuse of low-voltage CMOS design intellectual property (IP). Offering fully scalable highvoltage NMOS and PMOS devices, floating logic libraries as well as a best-in-class poweron resistance makes the 120 V high-voltage CMOS technology a compelling solution for fabless design houses and integrated device manufacturers (IDMs).

For additional information, contact: Ron Vogel (T) 408-345-1790 (E) ronald.vogel@austriamicrosystems.com (W) www.austriamicrosystems.com

Synopsys, a world leader in software and IP for semiconductor design, verification and manufacturing, and GLOBALFOUNDRIES, a leading provider of advanced semiconductor technology and manufacturing services, announced an agreement to develop the Synopsys DesignWare SuperSpeed Universal Serial Bus (USB) 3.0, USB 2.0, High-Definition Multimedia Interface (HDMI) 1.4 transmitter (Tx) and receiver (Rx), double data rate (DDR)3/2, Peripheral Component Interconnect (PCI) Express 2.0 and 1.1, Serial Advanced Technology Attachment (SATA) 1.5/3 Gbps and 6 Gbps, and Attachment Unit Interface (XAUI) physical layer (PHY) IP for GLOBALFOUNDRIES' 28 nm gatefirst high-k metal gate (HKMG) process technologies. The collaboration will enable mutual customers to differentiate their 28 nm designs with a high-quality IP portfolio at next-generation electronic targeted system-on-chips (SoCs). The long-standing relationship between the two companies has resulted in the successful development of DesignWare PHY IP from 180 nm to 32 nm process technologies. GLOBALFOUNDRIES and Synopsys are the first to announce the development of USB, PCI Express, DDR,

HDMI, SATA and XAUI PHY IP targeting 28 nm process technologies with scalability to future generations.

For additional information, contact: (T) 408-462-3900 (E) global.sales@globalfoundries.com (W) www.globalfoundries.com

MagnaChip Semiconductor, an Asiabased designer and manufacturer of analog and mixed-signal semiconductor products, announced that it now offers an enhanced process design kit (PDK) for 0.18 µm and 0.35 µm BCD technology which has been receiving industry-wide attention. The latest PDK features major advancements from three key perspectives: user environment, PDK content and design support. More specifically, functions such as a one-click download, PDK installer and auto-version matching enable rapid automatic setup of PDK conditions, creating a user friendly environment. A layout utility is also provided to support global net connection, seal ring and guard ring.

For additional information, contact: Robert Pursel

(T) 408-625-1262

(E) robert.pursel@magnachip.com

(W) www.magnachip.com

**Samsung Foundry** qualified the industry's first 32 nm high-k metal gate low-power (HKMG LP) process in May 2010, an optimized solution for customers' next-generation mobile and consumer products. Designers now can access this advanced leading-edge technology with proven IP and standard cell libraries in their development of advanced products. Volume production of 32 nm HKMG process products is scheduled for the beginning of 2011.

Samsung Electronics' foundry business is dedicated to supporting fabless companies and IDMs by offering full-service solutions, which encompass design kits and proven IP to full turnkey manufacturers, to achieve market success with advanced IC designs through foundry, application-specific IC (ASIC) and customer-owned tooling (COT) engagement. Samsung Foundry focuses on leading-edge process technology from 90 nm and below, and is currently in mass production at 45 nm and preparing next-generation 32 nm, 28 nm and beyond process technologies.

For additional information, contact: Timothy Kwon (T) 82-31-209-6024 (E) foundry@samsung.com (W) www.samsung.com/foundry

Virage Logic, the semiconductor industry's trusted IP partner, and **Semiconductor Manufacturing International (SMIC)**, the leading foundry in China, announced the

extension of their longstanding partnership in 40 nm low-leakage (LL) process technology. Building on the successful partnership that was initially established with 130 nm process technology, Virage Logic and SMIC have collaborated to provide mutual customers with highly differentiated IP for a broad range of SMIC's process technologies including 90 nm and 65 nm. Under the terms of the new agreement, SoC designers will have access to Virage Logic's SiWare memory compilers, SiWare logic libraries, SiPro Mobile Industry Processor Interface (MIPI) and Intelli DDR IP on SMIC's advanced 40 nm LL process. In addition, one key provision of this new agreement provides SMIC access to Virage Logic's advanced STAR memory system and STAR yield accelerator tools to accelerate the development, testing and yield enhancement of its 40 nm LL memory-related technology.

For additional information, contact: (T) 86-21-3861-0000 (E) webmaster@smics.com (W) www.smics.com

**SilTerra Malaysia** is a proud winner of the Product Excellence Award 2009, which was given by the Ministry of International Trade and Industry (MITI) of Malaysia. This award recognizes SilTerra's leadership position and innovation in high-voltage technology for single-chip display driver ICs used in display panels of digital still cameras, feature phones and smartphones.

SilTerra has been continuously investing in research and development (R&D) activities to enhance its technology competitiveness. New technology such as 180 nm BCDMOS and 180 nm V-Tr MOS technology was introduced for customers to design-in for power management applications used in light-emitting diode (LED) drivers, motor drivers, direct current-direct current (DC-DC) converters, lithium battery chargers and more. These technologies are developed for energy-efficient power management applications, which is inline with global green initiatives.

For additional information, contact: Meng Kong Koh (T) 604-401-4166 (E) mengkong\_koh@silterra.com (W) www.silterra.com

In June 2010, **Taiwan Semiconductor Manufacturing (TSMC)** reached an important milestone in the company's pledge to expand investment in Taiwan. This was achieved through the groundbreaking ceremony in Taichung's Central Taiwan Science Park for Fab 15, TSMC's third 12-inch (300 mm) Gigafab.

Fab 15 will be TSMC's third Gigafab, or fab with capacity of more than 100,000

12-inch wafers per month, and will also be TSMC's second Gigafab equipped for 28 nm technology. This will be TSMC's next "green fab" following Fab 12 and Fab 14, incorporating green concepts in energy conservation and pollution control in its design, including a process water conservation rate of 85 percent, reclamation of rainwater, recirculation and reuse of general exhaust heat, and development of solar power generation and LED lighting applications. TSMC's goal is to reach zero emissions of greenhouse gases.

TSMC is scheduled to begin equipment move-in for the Phase 1 facility in June 2011, with volume production of 40 nm and 28 nm technology products for customers in Q1 2012. Construction will be divided into four phases, and total investment over the next several years is expected to exceed NT\$300 billion

TSMC is the world's largest dedicated semiconductor foundry, providing the industry's leading process technology and the foundry's largest portfolio of processproven libraries, IP, design tools and reference flows. The company's total managed capacity in 2009 exceeded 10 million 8-inch equivalent wafers, including capacity from two advanced 12-inch GigaFabs, four 8-inch fabs, one 6-inch fab, TSMC's wholly owned subsidiaries WaferTech and TSMC China, and its joint venture fab Systems on Silicon Manufacturing (SSMC). TSMC is the first foundry to provide 40 nm production capabilities. Its corporate headquarters are in Hsinchu, Taiwan.

For additional information, contact: Ferda Mehmet (T) 415-308-7877 (E) ferda.mehmet@edelman.com (W) www.tsmc.com

**TowerJazz** announced its 5th annual customer-focused technology conference—the TowerJazz Global Symposium (TGS)—to be held October 28, 2010 at its Newport Beach facility. TGS will focus on design enablement and will feature an industry outlook keynote from Gartner.

The company also announced its expanded business relationship with Vishay Siliconix to include increased production of its high-voltage power metal-oxide semiconductor field-effect transistors (MOSFETs) and super junction FET power MOSFETs.

TowerJazz was selected by Tego to manufacture its high-memory radio frequency identification (RFID) chips to be used by Airbus for improved aircraft maintenance and logistics. In addition, Canesta chose TowerJazz for its CMOS image sensor (CIS) technology to manufacture 3-D image

sensors for consumer desktop computing, TV and entertainment applications.

TowerJazz also announced its further momentum in Korea with its global technology symposium and participation at the Institute of Electrical and Electronics Engineers (IEEE) International Memory Workshop to present its industry-leading non-volatile memory (NVM) technology.

For additional information, contact: Melinda Jarrell

(T) 949-435-8181

(E) melinda.jarrell@towerjazz.com

(W) www.towerjazz.com

(UMC) Microelectronics United partnered with Elpida and PTI to develop a fully integrated through-silicon via (TSV) solution suitable for a wide range of applications. Leveraging UMC's leadingedge logic technology and logic design interface with Elpida's dynamic random access memory (DRAM)/TSV technology and PTI's packaging and testing, this joint development project will allow UMC to provide foundry customers with a total solution for their 3-D IC designs that includes logic + DRAM interface design, TSV formation, wafer thinning, testing and chip stacking assembly. The resulting technology is expected to help fabless customers increase cost competitiveness, improve logic yield impact and accelerate entry into the 3-D IC market.

For additional information, contact:

(T) 886-3-578-2258

(E) sales@umc-usa.com

(W) www.umc.com

X-FAB recently announced the industry's first 100 V high-voltage 0.35 µm pureplay foundry process. It enables a new class of reliable, high-performance battery monitoring and protection systems for battery management. It is also ideal for power management applications and for ultrasonic imaging and inkjet print head apps using piezoelectric drivers. In addition, X-FAB added new and enhanced N- and P-type double-diffused metal-oxide semiconductor (DMOS) transistors with 45 percent lower on-resistance for multiple operating voltages up to 100 V, lowering the silicon footprint by up to 40 percent and thus reducing die costs. Other device enhancements include Schottky diodes, 20 V and 100 V high-voltage capacitors, and bipolar transistors.

For additional information, contact:

Anja Noack

(T) 49-361-427-6162

(E) anja.noack@xfab.com

(W) www.xfab.com

■

Performance. To get it right, you need a foundry with an **Open Innovation Platform™** and process technologies that provides the flexibility to expertly choreograph your success. To get it right, you need TSMC.

Whether your designs are built on mainstream or highly advanced processes, TSMC ensures your products achieve maximum value and performance.

**Product Differentiation.** Increased functionality and better system performance drive product value. So you need a foundry partner who keeps your products at their innovative best. TSMC's robust platform provides the options you need to increase functionality, maximize system performance and ultimately differentiate your products.

**Faster Time-to-Market.** Early market entry means more product revenue. TSMC's DFM-driven design initiatives, libraries and IP programs, together with leading EDA suppliers and manufacturing data-driven PDKs, shorten your yield ramp. That gets you to market in a fraction of the time it takes your competition.

**Investment Optimization.** Every design is an investment. Function integration and die size reduction help drive your margins. It's simple, but not easy. We continuously improve our process technologies so you get your designs produced right the first time. Because that's what it takes to choreograph a technical and business success.

Find out how TSMC can drive your most important innovations with a powerful platform to create amazing performance. Visit **www.tsmc.com**

Open Innovation Platform

## HIDDEN LOGISTICS AND FULFILLMENT COSTS IN THE SEMICONDUCTOR SUPPLY CHAIN

MARTA GARCÉS, VICE PRESIDENT, OPERATIONS, ADD SEMICONDUCTOR

ffective supply chain management enables companies to be more competitive in the world of manufacturing by reducing costs and improving customer service. The main purpose of a supply chain is, in fact, to make products available to customers in the right quantity, at the right time, with the best quality and in the most cost-effective manner.

When speaking about a semiconductor start-up's supply chain needs, the process becomes even more complex and critical as not only standard logistical problems and costs must be taken into account, but also storage, handling of the final product, and packaging quantities that may be limited by wafer size, thus making it a critical point to better manage the supply chain so as to handle possible quality problems reported by end customers. All these facts make it challenging for semiconductor start-ups and third-party logistics partners to implement strong, flexible supply chains.

#### The Everyday Problems of Global Sourcing

Today's modern semiconductor industry requires properly established and organized supply chains set up for maximum efficiency so as to avoid problems. The semiconductor market is truly global. Its major foundries primarily located in Asia and the United States ship sensitive materials all around the world using distributors that may not be familiar with the foundries' special characteristics such as specific security measures and tamper-proof locks. The market demand variability for these types of products is very high, generating different situations, from allocation problems to standard lead times and overstock management when demand falls abruptly, creating an

uncertainty that makes logistics and supply chain planning a critical step.

A supply chain exhibiting no problems can still be in danger if suddenly faced with situations as simple as a storm or as critical as a political disruption or a strike. Therefore, even if a company outsources freight management to a third party, it must always know the status of what has been shipped or is due to be shipped at each stage of the supply chain. A lack of readily available information can also cause a company to not identify and solve problems in time.

If a supply chain is not correctly managed, a number of hidden effects may appear, all of which usually result in the company losing money and efficiency. Quality control throughout the chain is also of high importance, from material quality to the adequate packaging of goods and going through adequate and complete customs documents. The failure to meet any of these requirements can lead to a shipment delay or even damage the final product.

Another important point is the bureaucracy involved in shipping product. A misunderstanding of a country's custom rules and regulations can incur improper freight costs and inefficient deliveries. With overseas purchases being a daily routine in the semiconductor market, purchasing companies must work closely with their suppliers and make sure distributors have complete knowledge of all rules and regulations so as to avoid unexpected issues.

Also, bad planning, bad maintenance of safety stock inventory and last minute orders from customers due to lack of critical scheduling information at the fabless company can lead to very tight deadlines, delaying or changing shipments. This always involves the necessity of

using expedited transportation services which can double the cost of regular freights.

How a company manages its supply chain defines in some way its business, and therefore must continually study how to control and improve all aspects involved. A company's image can be seriously damaged by missed deadlines or late deliveries, putting them in a difficult position as they will have to explain to their customer how and why the system went wrong. That is why having all needed information readily available is crucial as it allows the chain to be informed about possible delays or problems.

#### Fabless-Specific Problems

Fabless start-ups must take into account not only standard logistics costs, but also costs that many times seem to be absorbed by the day-to-day work. These costs should be considered hidden logistic costs when analysis of margins and revenues is so critical in the early stages of company growth. The importance of knowing the real logistics costs is vital to obtaining the true financials of a company. It must be aware that these costs not only include those related to shipping.

The first barrier fabless companies encounter is the minimum order quantities (MOQ) companies must acquire even in ramp-up production. These quantities apply to those companies creating new business and having a small number of customers that are only testing new, possible suppliers and thus using small quantities of product. This requires a great effort in logistics such as a bigger warehouse to store incoming product, more days of inventory as it will take longer to sell product, and handling sensitive components during adequate installations with an ill-prepared staff.

This potential problem escalates when using special manufacturing processes. To maintain quality and traceability, each wafer manufactured is treated as a different lot, which means two realities must be taken into account:

- The number of chips on each wafer is not the same in every production as there is an indefinite number of wasted dies that does not remain the same from one production to another.

- To maintain product quality and traceability during the entire process, chips obtained from different wafers must not be packaged together in the same box so they can be uniquely identified and followed throughout the supply chain.

These issues also affect logistics in two ways:

- The number of packages received in each shipment and the quantity included is not known in advance and is difficult to control as it may vary from one production and/or delivery to the next. Therefore, expected delivery costs and warehouse placement can differ.

- It is difficult to transmit MOQs to final customers so as to reduce the internal handling of product, as the expected quantity in each box is not always the same and can't be known in advance.

Due to this matter, another and more critical problem arises—handling critical product. There is great risk involved if a fabless start-up receives an incorrect packaged quantity from its supplier, for example, and is therefore forced to open the original sealed package and manipulate product to make sure the correct quantity is shipped to its customer. The components could become damaged if the staff moving them does not possess the necessary skills and if they are

moved under unfit conditions. There is also the difficulty of keeping the remaining product not shipped in a proper environment in terms of humidity, temperature and packaging. The company should invest in equipment such as vacuum packaging machines and small strapping machines, in material such as antistatic bags and extra trays, and in personnel dedicated to these tasks so the product is stored under the best conditions.

Obviously, these must be considered extra logistics and supply chain costs, not only taking into account delivery and warehouse costs, but also personnel costs. The company must be aware of these extra costs as they are many times hidden from those in charge of calculating the final product cost. Is it the responsibility of logistics and operations personnel to calculate the time and money invested in these everyday jobs so they can be added to the final cost of the product?

#### Some Possible Solutions

All these problems have to be seriously considered, as the supply chain can help emerging companies get introduced in new markets and is the most significant source of cost savings when all the previous issues mentioned are handled in the most efficient way.

Third-party logistics partners can assume some of the global sourcing issues that companies face such as warehousing and partnering with distributors. Direct relations with foundry, assembly and test subcontractors are also a necessity to have full visibility and traceability of product throughout the supply chain process and to respond to customer information requests in real time. These options, combined with adequate metrics, a good traceability system and new electronic tracking methods used by distributors to follow shipments in real time in each stage of delivery, give companies tools to control the supply chain. They also make it easier for companies to deal with future problems, solving them in the best way and in the shortest amount of time without affecting the end customer.

Problems inherent within start-ups are not easy to solve as only company growth can diminish them. It is a constant challenge for them to manage and reduce logistics costs. Efforts to reduce costs include, among others, negotiating directly with customers to adjust quantities to be delivered, minimizing the handling of material; planning supplier orders and shipments to be as adjusted to reduce inventory costs; and strengthening the structure of the company with the technical tools and personnel needed to face problems that must be managed once it is established and leaves its start-up condition.

The company must finally have the agility and ability to react promptly and appropriately to market conditions and have a strong, flexible supply chain. There are many tools and ways to achieve this. It is only a matter of choosing the correct ones and putting them to use within the company.

#### About the Author

Marta Garcés has a telecommunications engineering degree from the University of Zaragoza. Before joining ADD Semiconductor's staff, she worked for Siemens as corporate coordinator in the areas of quality, environment and European Foundation for Quality Management (EFQM), and in Kepar Electrónica firstly as R&D&i manager and later as project and international purchasing manager. At present, she performs the function of vice president of operations in ADD Semiconductor. You can reach Marta Garcés at marta.garces@addsemi.com or +34 690 014 749.

Advantest introduced its scanning electron microscope (SEM)-based critical dimension (CD) measurement system for photomasks. Advantest's E3610 and E3620 CD-SEM advanced mask metrology tools enable photomask manufacturers to measure the critical dimension of the miniature-sized patterns in a photomask and assure accuracy in semiconductor manufacturing. These systems offer the precision and linewidth repeatability required to provide continuous yield improvement at the 65 nm and 45 nm production nodes, as well as support for 32 nm and 22 nm process development. The best-in-class E3610 and E3620 utilize Advantest's unique electron optical column design, enabling accurate CD control. They boast superior long-term operating stability and CD variation of less than ±1 nm, and are backed by the Advantest brand and the company's renowned worldwide support infrastructure.

For additional information, contact:

Greg Self

(T) 480-888-7700

(E) g.self@advantest.com

(W) www.advantest.com

Amkor Technology and Texas Integrate and expective company in the packages—shrinking bump pitch up to 300 percent compared to current solder bump flip-chip packages—shrinking bump pitch up to 300 percent compared to current solder bump flip-chip packaging costs of IC devices with fine-pitch input/output (I/O) pad structures of less than 50 µm, this proprietary technology platform also boosts performance, making it ideal for wireless and embedded processing applications based on plated copper pillar bumping and assembly technology.

Working together, Amkor and TI rapidly developed, qualified and deployed this new package platform that will not only address TI's flip-chip package needs

GLOBAL SEMICONDUCTOR INDUSTRY. E3610 and E3620 CD-SEM advanced mask metrology tools enable photomask manufacturers to measure the critical

for the next decade but will also serve as a game changer for the industry. This new lead-free technology enables the use of flip-chip interconnection at fine pad pitches (50 µm and smaller) using finepitch copper pillar bumping and a newly developed assembly process which acts as the platform interconnect technology for integration with next-generation advanced silicon nodes. It also typically reduces substrate layer count as compared to standard area array flip-chip, yielding a low-cost package solution. The package was developed for very thin die, which, when combined with the low standoff height of the copper pillar bump itself, reduces package height.

For additional information, contact: Lee Smith (T) 480-821-2408 ext. 5381 (E) lee.smith@amkor.com (W) www.amkor.com

**DA-Integrated** is the semiconductor industry's first and leading provider of comprehensive IC development and supply engineering services. DA-Integrated features a full suite of tools and expertise of a fabless semiconductor company, offered as pure-play services, complementing customers' capabilities.

Finding the right provider for production testing of low-volume and high-complexity ICs is always a challenge, especially when global capacity is constrained. DA-Integrated's test operations group has grown to meet this increased demand. The provides competitively priced production capability targeted specifically at this market segment. Access to support from the company's design, test development and supply engineering experts enhances the service, making DA-Integrated the world leader for engineering sampling, pre-production, reliability testing and low to medium volume production.

For additional information, contact: Scott Bulbrook (T) 613-592-2233 ext. 227 (W) www.da-integrated.com

(EAG)

team

**Evans** Analytical Group's release-to-production (RTP) provides engineering service and support from early chip design to volume production in the areas of test program development and product engineering; test time rental on all major automatic test equipment (ATE) platforms; reliability and environmental qualification; electrostatic discharge (ESD) and latch-up testing; printed circuit board (PCB) layout and hardware design; failure analysis; focused ion beam (FIB) circuit edit and debug; electron microscopy (transmission electron microscopy (TEM), SEM, dual-beam FIB/SEM); and equipment calibration and repair services. Coupled with 30 years of experience in materials characterization and surface analysis, EAG offers the broadest range of solutions of any commercial lab

network. EAG offers its customers a highly customizable and flexible service model. The company believes that each customer's needs require the right combination of resources, and outsourcing cannot take a one-sizefits-all approach. Many of EAG's fabless customers rely heavily on EAG's integrated model to support their product flow from conception to volume production, requiring full engineering support across multiple disciplines and services. EAG's larger fabless and integrated device manufacturing (IDM) customers are utilizing this model to support specific projects as a compliment

to their own resources. With the breadth of engineering expertise and services and continued commitment to investment in technology, EAG is the partner to keep.

For additional information, contact: Aram Sarkissian (E) aram@eaglabs.com (W) www.eaglabs.com

Through the years, **LingSen Precision Industries (LPI)** has emerged as a leader of semiconductor subcontract assembly in Taiwan. LPI's engineering and production teams have earned a formidable reputation worldwide for providing high-quality product lines and reliability in its total solution. LPI's assembly capabilities are proven throughout the U.S., Europe, Asia and China. The company's deliverables include micro-electromechanical system (MEMS) quad flat no-lead (QFN) packages, MEMS pressure sensors and MEMS microphones.

The MEMS QFN package is a plastic encapsulated package with exterior leads around the bottom periphery to provide short electrical connection to the printed wiring board (PWB). The package also provides excellent thermal performance by having the die attach paddle exposed on the bottom of the package surface to provide efficient heat path when soldered directly to the PWB.

The MEMS pressure sensor is a wire-bonded and lid seal on pre-mold leadframe packages, and can be used in medical instrumentation products.

The MEMS microphone is a wire-bonded and cap seal on substrate system-in-packages (SiPs), and can be used in communication and consumption products.

For additional information, contact: Lilian Lin

(T) 886-4-2533-5120 ext. 5174

(E) lilianlin@lingsen.com.tw

(W) www.lingsen.com.tw

**MASER Engineering** offers Safe Launch support to the automotive semiconductor industry. During the first ramp-up phase of new ICs in automotive applications, the manufacturer has to prove device durability. MASER Engineering supports fabless IC manufacturers with extended monitoring of the devices during Safe Launch burn-in. A dedicated setup will stress the devices beyond the observable level with ATE final test. Chips with power dissipation levels of 1 watt or beyond are exposed to a power

temperature cycling where long-term stability is proven with multiple on/off starts at very fast linear temperature ramps, up to 10 K/min. Both test methods are formulated in the dedicated automotive standard Automotive Electronics Council (AEC)-Q100. MASER Engineering is fully equipped to address all related qualification tests to this standard as a service.

For additional information, contact: Kees Revenberg (T) 31-53-480-26-81 (E) kees.revenberg@maser.nl (W) www.maser.nl

MVTS Technologies is a global fullservice provider of refurbished ATE to the semiconductor industry. MVTS provides support and service for a selection of legacy Credence, LTX, Teradyne and Verigy ATE worldwide, configured and refurbished to customers' specifications. With a global team of field service representatives, MVTS is confident in providing each customer with maintenance, installations, de-installations and repairs. In addition, the company has a broad range of value-added services such as turnkey applications, subcontract printed circuit board (PCB) repair and essential test cell consumables.

For additional information, contact: Ross Martindale

(E) ross.martindale@mvts.com

(W) www.mvts.com

Presto Engineering, an International Organization for Standardization (ISO) 9001 company, delivers Design Success Analysis, comprehensive semiconductor test and analysis solutions to IDM and fabless companies. Operating from hubs in Silicon Valley and Europe, the company's business is focused on helping to improve the speed and predictability of new product releases.

Presto combines unique technical expertise, extensive industry experience and leading-edge ATE for system-on-chip (SoC) and radio frequency (RF), along with reliability, FIB and failure analysis/fault isolation services to offer a complete product engineering solution designed to complement customers' internal resources.

During 1H 2010, Presto established new hubs in Europe focused on failure analysis and reliability services (Normandy hub, ex-NXP lab) and ATE services, covering test program development and engineering bring-up support for both wafer and packaged parts (Grenoble hub).

Presto is now offering specialized RF characterization and testing services from its Silicon Valley and Grenoble hub, covering wafer-level, packaged part and multichip modules (MCMs). The company's lab has the ability to use high-frequency test and measurement equipment (i.e., network analyzer, pattern generator, bit error rate test (BERT)), as well as RF ATE (Roos Instruments Cassini) supporting direct current (DC) to 100 GHz source and measure. Presto can also assist with test program development, probe card design (GGB and Cascade Pyramid) and automatic handler support. Presto's lab in Grenoble has the Verigy 93 K Pin Scale RF test equipment as well as 300 mm wafer probe support.

For additional information, contact: (T) 408-434-1808

(E) info@presto-eng.com

(W) www.presto-eng.com

STATS ChipPAC's low-cost flip-chip (LCFC) technology utilizes copper column bump to deliver a powerful packaging solution at a dramatically reduced cost. LCFC technology delivers flip-chip packages at price points below wire-bond packaging due to its innovative routing-efficient interconnection structure, simplified substrate design and cost-effective mold underfill process. The unique structure of LCFC when combined with copper column bump achieves an even lower cost solution with higher routing densities and is scalable to finer bump pitches. Copper column bumps enable a higher I/O density with a much finer pitch between the columns than standard solder bumps, along with a higher resistance to electromigration. Although copper column is a hard bump material that can typically cause damage to low-K (ELK) layers in finer silicon nodes, the LCFC interconnect structure dramatically reduces the mechanical stress on silicon subsurface layers, resulting in the elimination of the ELK damage phenomenon commonly observed in sub-45 nm silicon nodes.

For additional information, contact:

Lisa Lavin

(T) 208-867-9859

(E) lisa.lavin@statschippac.com

(W) www.statschippac.com

■

## INTERNATIONAL CHALLENGES IN ENVIRONMENTAL COMPLIANCE AND SUPPLY CHAIN SUSTAINABILITY

Tom Krawczyk, Compliance Manager, Conexant Systems Inc.

Bob Warren, Director, Packaging Engineering & Assembly Manufacturing, Conexant Systems Inc.

ive years ago, if you asked someone in the electronics industry to explain the meaning of "environmental compliance," the answer would have been fairly straightforward. Environmental compliance meant meeting the European Union's (EU) recycling requirements identified in the Waste Electrical and Electronic Equipment (WEEE) directive and meeting the EU's substance/ threshold limit requirements of the Restriction of Hazardous Substances (RoHS) directive which took effect on July 1, 2006. The environmental management standard of record was the relatively well-known International Organization for Standardization (ISO)14000:1996.

Fast forward to 2010 and ask the same question, and the answer is entirely more complex and difficult. Today, environmental compliance is not solved by crossing a well-defined finish line. Over the past few years, there has been an explosion of new environmental requirements across the globe, with a myriad of new restrictions and reporting requirements being imposed on the entire electronic supply chain. Many of these regulations are still evolving, most are widening in scope, and some are interpreted or enforced differently in various global regions. In addition to regulations, there are additional requirements being imposed by large original equipment manufacturers (OEMs) that are often more rigid and extensive than those being pushed by governmental agencies. All of this is forcing electronics companies and their suppliers to deal with an overwhelming set of environmental compliance variables that vary from customer to customer, product line to product line and region to region.

#### An Explosive Growth of New Regulations

It has been said that the massive number of new environmental regulations that are coming into force can be best described as a tsunami—many are coming in from distant shores, often with little warning. To understand the magnitude of dealing with environmental compliance today, consider what has happened in the last few years:

- China introduces their version of RoHS adding new labeling requirements and environmentally friendly use period (EFUP) rules, which specify the period of time before any of the RoHS substances are likely to leak out and cause possible harm to health and the environment.

- California introduces their own RoHS laws prohibiting an electronic device from being sold or offered for sale in California

- if that device is prohibited from being sold or offered for sale in the EU due to the presence of lead, mercury, cadmium or hexavalent chromium above certain maximum concentration values (MCVs).

- ISO releases an amended version of its environmental management standard ISO14001:2004.

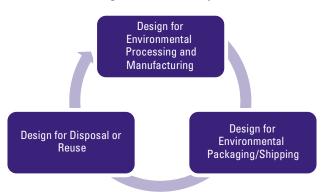

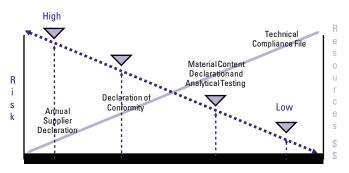

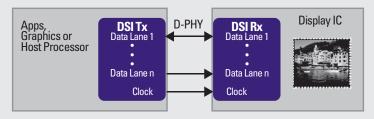

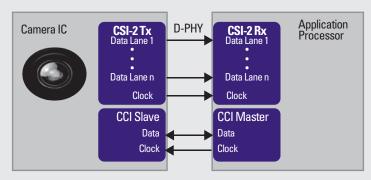

- The EU introduces Registration, Evaluation, Authorization and Restriction of Chemical Substances (REACH), ultimately regulating an estimated 30,000 chemicals and banning or restricting any substances of very high concern (SVHC). Several revisions have already been made to the SVHC list of chemicals/compounds. There are currently a few dozen SVHCs for semiconductor "articles," but the list is expected to grow to 300 or more.